# **NTT Technical Review**

# March 2011 Vol. 9 No. 3

3

# **NTT Technical Review**

### March 2011 Vol. 9 No. 3

### Front-line Researchers

Makio Kashino, Senior Distinguished Researcher, NTT Communication Science Laboratories

### Feature Articles: System LSI Design for Broadband Optical Access Network Systems

System LSI Design Technology for Communications Networks

Cooperative Hardware/software Design Technology

MAC LSI Design Technology for Optical Access Communications

Design Verification Using Field-programmable Gate Arrays for Optical Access Communications SoC

10-Gbit/s Burst-mode Receiver Integrated Circuits for Broadband Optical Access Networks

## Feature Articles: R&D of Optical Component Technologies for 100-Gbit/s Digital Coherent Communications

Optical Device Technologies for Future Network Evolution

Wavelength-tunable Lasers for Next-generation Optical Networks

Multilevel Optical Modulator Utilizing PLC-LiNbO<sub>3</sub> Hybrid-integration Technology

100-Gbit/s Optical Receiver Front-end Module Technology

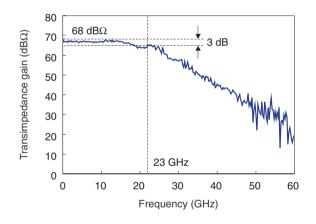

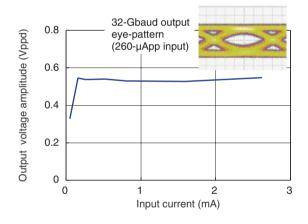

Photodiodes and Transimpedance Amplifiers for 100-Gbit/s Digital Coherent Optical Communications

### **Regular Articles**

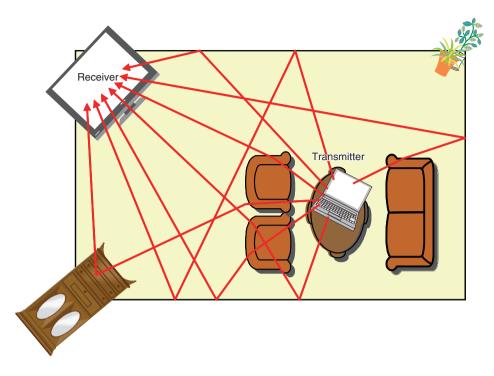

Antenna Model and Its Application to System Design in the Millimeter-wave Wireless Personal Area Networks Standard

Compressed Sensing Technology for Flexible Wireless System

### **Global Standardization Activities**

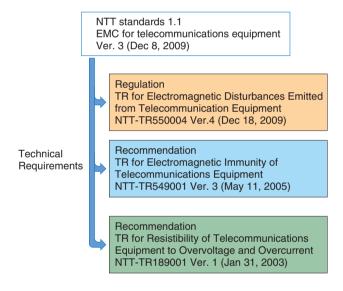

Electromagnetic Compatibility Standardization Activities in the Telecommunication Field at the 2010 IEC/CISPR Seattle Meeting

Papers Published in Technical Journals and Conference Proceedings

Papers Published in Technical Journals and Conference Proceedings

### **Front-line Researchers**

# **Toward Life-enriching Technologies**

### Makio Kashino Senior Distinguished Researcher NTT Communication Science Laboratories

Makio Kashino, an NTT Senior Distinguished Researcher, has enjoyed Japanese and Chinese classical literature since childhood. He has been particularly influenced by the *Zhuangzi* (classical Taoist book) by the Chinese author of the same name and the *Hojoki* (An Account of My Hut) by the Japanese author and poet Kamo no Chomei. Both of these philosophize about the impermanence of worldly things. We asked Dr. Kashino, a unique researcher who attempts to explain *hearing* and *communication* from the viewpoints of psychology, neuroscience, and information science, to tell us about the manner, significance, and future of his type of research.

### Probing the human mind via an integrated approach

### *—Dr. Kashino, could you first give us some background to your research?*

Since entering NTT, I have been exclusively researching human perception with a focus on human auditory mechanisms. While hearing a sound may appear to be easy, it is actually a very complex process. If you visit the Illusion Forum website [1] that we have created, it's plain to see, or rather, it's plain to hear, that this is so. In hearing, a variety of peculiar things can occur; for example, you might hear nonexistent sounds or hear the same sound in different ways. Such phenomena are manifestations of brain functions that enable humans to adapt to their surroundings. In my research, I have been working to elucidate these clever neural mechanisms.

In this kind of research, I have found it essential to integrate three approaches. The first is to quantify the features of human perception, as in the case of illusions such as those that I just mentioned. The second is to study the workings of the human brain and nervous system that serve as the hardware for achieving those features. And the third is to comprehend the principles of information processing that make those features possible in the first place. In other words, we can begin to explain the mechanisms of *hearing* through the three fields of psychology, neuroscience, and information science. Let me make an analogy here. If I were to research the flight of birds, I could not simply analyze wing strokes and the structures of wings and muscles: I would also need to understand the principles of flight, that is, of aerodynamics. Only then would I be able to apply the knowledge gained to aircraft.

### *—What is your current research theme?*

Well, my research is still centered on hearing, but I am currently working to broaden the scope of my studies. It occurred to me that this integrated approach that I've developed could perhaps be used to scientifically explain heretofore elusive problems like preferences and feelings. Let me give you three specific examples of this expanded research in our group.

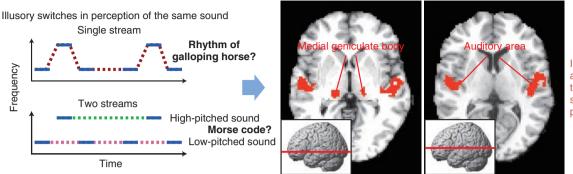

Identifying neural activity linked to the formation and selection of perception

Fig. 1. Uncovering neural information-processing principles from an illusion.

First, in relation to hearing, we're researching the neural mechanism that enables one to selectively listen to only what one intends to hear in a mixture of many sounds. (Fig. 1). This cocktail party effect is often said to be an outstanding feature of human hearing, but it tends to be deficient in some groups of people such as the elderly and hearing impaired. A hearing aid often just amplifies noise as well, resulting in no substantial improvement in hearing. In our research on testing hearing ability, we have found that some people who show no apparent abnormalities in an ordinary otological test may sometimes have difficulty hearing a sound in the presence of competing sounds. We have been investigating a new hearing test that can identify such people and we are close to finding the cause of this phenomenon.

Cases in which a hearing problem can hinder an individual's full participation in society despite ample skills or motivation are expected to multiply as we enter the aging society. The creation of a barrier-free society is a key objective of information and communications technology (ICT), and I think that we can help give many people a greater sense of purpose in their lives if we can develop a hearing aid that lets them hear only what they prefer to hear.

Second, we're researching ways of quantitatively predicting preferences in relation to music, design, etc. For example, a person may respond favorably to certain kinds of music saying something like "that's good" or "I like that music." In such a case, the music is probably somewhat familiar and not completely new to the user. In other words, music that is all too common for the listener can be boring while something that is too novel or original may turn the listener off. So how new should something be to be the most attractive? The ability to derive this in theoretical terms would no doubt bring big changes to the way that products are designed and advertised. Traditionally, design and advertising have depended on the experiences and hunches of those in charge, but a systematic approach could make the process more efficient. All this might sound too good to be true, but I believe that such predictions should be possible to some extent by applying the principles of neural information processing. What we need here is some kind of proof, and to this end, we are conducting various types of experiments.

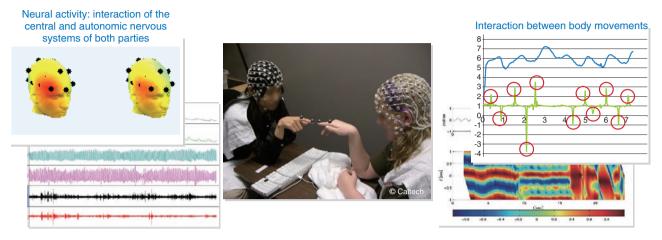

Third, we're researching subliminal signals and body language (**Fig. 2**). In interpersonal communication, information that cannot be directly conveyed by words plays an important role. In particular, the atmosphere between two people is often created by slight changes in facial expression or tone of voice that are usually unnoticeable to either party. This type of unconscious exchange of implicit information between two people helps to establish smooth communication. We are now working to explain the actual mechanisms of nonverbal communication through experiments that measure slight body movements, physiological changes, and neural activity during interpersonal communication.

Such implicit information was probably discarded as unnecessary in past technologies because, in conventional communication systems, it was sufficient to assess whether a phrase like "thank you" was actually heard as "thank you". As a consequence, information that could convey whether this "thank you" was actually an expression of gratitude or a sarcastic remark was simply ignored. However, if such elements of communication can be clarified, it should be possible to achieve a form of communication with a high level

- Implicit interpersonal information (IIPI) is unconscious (implicit) body movements or physiological responses made by one or both parties while they are communicating with each other.

- · Basic hypothesis: IIPI is the foundation of subliminal signals.

- IIPI and its underlying neural and nervous-system activities can be used to clarify and appropriately control emotions and the state of communication.

Supported by JST CREST (research representative: Makio Kashino (NTT); coworkers: Shinsuke Shimojo (California Institute of Technology) and Katsumi Watanabe (The University of Tokyo))

of presence such as in a videoconference system connecting remote locations via the network.

### Toward a career in hearing research from an attraction to temporal flow

### *—What moved you to become a researcher in the field of hearing?*

Most of my instructors and seniors in my university research laboratory were researching topics related to vision. For example, they were studying the response of goldfish retina cells to light, the neural activity of monkeys, and human visual illusions. Moreover, my advisor was researching mathematical models of visual pattern recognition. I learned a lot about methodology from my involvement in these studies. However, I had developed an interest in sounds through listening to a wide variety of music and building electronic gadgets from discarded parts starting in my elementary school days, and what I really wanted to research was the perception of sound, or in other words, hearing. In Japan, there were not many researchers in this area. I could therefore pursue this interest to my heart's desire, which suited me perfectly.

In addition, since my childhood, I've been inter-

ested in how one captures things that change and the nature of impermanence. Living things move and change, and this change occurs continuously together with a *temporal flow*. I found this flow to be very appealing.

At the same time, I thought that sound, which cannot exist without incessant change, is closer in essence to flow than vision. This is also one factor that led me to specialize in hearing.

### -What kind of researcher do you think you are?

I believe that my motivating force is a philosophical awareness of problems, but in my case, pure speculation by itself has its limits. Come to think of it, I've enjoyed doing experiments since my childhood. What I like about experiments is that they do not always turn out as expected. Of course, if we establish a certain hypothesis, perform an experiment to test it, and obtain a result that meets our expectations, then it's time to celebrate! But this could also be boring in the sense of a pre-established harmony as discussed in philosophy. An unexpected result, on the other hand, can broaden our scope of thought and be much more interesting. If we give lots of thought to an unexpected result, we may find it to be the most natural outcome after all. At the same time, I also enjoy theory, and it gives me great pleasure to be able to provide a uniform explanation for perplexing things or unrelated things through simple principles. In short, a continuous cycle of theory and experiment is essential to my integrated approach.

### Baseball and work: unconditioned nature

### *—I've heard that pitching—as in baseball—is a hobby for you.*

Yes, that's right, but not in the sense of playing sandlot baseball just for fun. What I pursue is simply the act of throwing with great devotion. I do this every day if possible. But please don't ask me why I do it. Perhaps I find the act of throwing one ball after another interesting like the cycle of hypothesis and experiment. At any rate, one throw out of maybe 30 or 40 surprises even me. But if I get all excited and try to do it again, I end up making a throw that's not nearly as good. This is very strange.

A ball is thrown not by the power of one's arm but rather by accelerating the tips of one's fingers to the utmost through power generated by the movement of one's weight and the twisting of one's lower body. An arm that is simply shaking looks exactly like a flexible whip. However, when you consciously attempt to throw a fast ball, excessive power will enter your arm and shoulders, and at that instant, the power that would normally be conveyed by the lower part of your body and by your trunk will fall behind. It so happens that when I fall into some kind of rhythm and stop worrying about my next pitch, I get this sensation of being driven only by gravity and inertia and I end up making some incredible pitches while feeling quite relaxed.

Perhaps this is an example of *unconditioned nature* as described in the *Zhuangzi*. In some way, you can

perform your best when you lose the self and do not fight the providence of nature (when you go with the flow). If, by plain luck, you were to throw a great ball, it could then be said that you already had it in you to do so, but the problem now is whether you can invoke that ability at will. In other words, the problem is how to coordinate with good timing the roughly 400 skeletal muscles in the human body without mutually cancelling out the flow of power through them. It is said that the great baseball player Ichiro, though having a thin figure, can outperform other major-league players far superior in strength by optimizing muscle coordination.

For this reason, I do not go out of my way to build up my muscles, but look for ways of improving my coordination. I feel as if I'm advancing little by little, and I don't think it's altogether unrealistic to aim for a pitching speed of 130 km/h at 50 years old.

The importance of natural coordination should also hold true in work. The more one thinks about having to go all out, the more one's natural pace will fall apart without any gain in performance. This also applies to management in an organization. If superiors in their excitement to excel assign useless work, subordinates are bound to become exhausted. Whether it be an individual or an organization, I don't think that intrinsic potential can be tapped in this way. It must be said, however, that working in a natural way is really difficult.

### **Future outlook for ICT**

### —What do you think is the future of ICT?

The research that I conduct aims to elucidate this providence of nature. In other words, I am involved in scientific research, but at the same time, I am deeply concerned with the future of ICT. As a basic belief, I feel that ICT is not simply a means of making life more convenient—it must also serve to enrich the lives of human beings. And to this end, ICT must help people achieve their intrinsic, natural state of being. Accordingly, basic research on clarifying the providence of nature in relation to human beings should, in the end, lead to a form of ICT that works to enrich people's lives.

It would be natural to think that ICT could be used to good effect by establishing a barrier-free society and to assist the sensory and motor functions of the elderly. But on a long-term basis, what if such measures turned out to actually weaken brain functions? My answer to this is to make use of nature and isolate and enhance intrinsic neural and physical functions. Ideally, there would be a set of tools that can do just that.

While it is easy to measure the efficiency and physical performance of just about any product, it is difficult to measure the extent to which such a product actually enriches a person's life. It is exactly this point that should become a matter of importance in the years to come. The provision of top specifications and high quality is a matter of conscience for certain types of enterprises, but as a natural precondition for this, I believe that products should be designed taking into account feelings and perception so that possessing a product brings some delight into a person's life. For this reason, feelings and perception should be subjects of discussion in scientific and engineering fields.

Today, Japan provides the fastest and most inexpensive broadband environment in the world. The optical-fiber service area covers 90% of all households, but no more than 30% are actually making use of these services. Why are the remaining 60% not using broadband? No doubt price is one factor, but could another factor be not actually being able to feel the value of broadband? Do these households perhaps feel that their current way of using the web, email, and weblogs (blogs) is more than sufficient? If a household were to upgrade to broadband or introduce ICT, to what extent would the lives of its family members be enriched? Customers don't think in these terms, and neither, I suspect, do service providers. Here, remote medicine, to give one example, could be used not simply as a means of transmitting digital medical records but also to encourage interest in broadband and ICT. So there's still hope. I feel strongly that disseminating such a concrete image of broadband services should be the responsibility of us basic researchers.

### To young researchers

*—Dr. Kashino, please leave us with a message for young researchers.*

It is often said that originality is essential for researchers, but I feel that the meaning of this is sometimes misinterpreted. In particular, in today's competitive society, we are made to feel like a failure if we don't do something different from other people, and we start out by thinking "How can I do something unique?" However, great baseball players like Nomo and Ichiro were not great just because they had different forms of play. Each worked ceaselessly to optimize his individual performance and simply came to adopt that form as a result. While appearing to be unique at first glance, their forms of play owe a lot to the providence of nature.

I think this also holds true in research. The etymology of the word original is origin, and the origin of ICT is to find out what is needed to enrich people's lives. If we return to this origin and listen carefully to the voice of nature, I think that we should be able to perform great work.

### Reference

[1] Illusion forum (in Japanese). http://www.brl.ntt.co.jp/IllusionForum/

### Kashino Makio

Senior Distinguished Researcher, NTT Communication Science Laboratories.

He received the B.A., M.A, and Ph.D. degrees in experimental psychology from the University of Tokyo in 1987, 1989, and 2000, respectively. He joined NTT in 1989. He has also held various posts outside NTT including those of visiting scientist at the University of Wisconsin (1992– 93), visiting professor at Tokyo Institute of Technology (2006–current), invited professor at l'Université Paris Descartes (2008), and project leader of a CREST (Core Research of Evolutional Science & Technology) project of the Japan Science and Technology Agency (JST) (2009– current). His research field is cognitive neuroscience of human perception and communication.

# System LSI Design Technology for Communications Networks

### Tsugumichi Shibata<sup>†</sup>, Mamoru Nakanishi, and Mamoru Kitamura

### Abstract

The first set of Feature Articles in this issue describes research and development of system large-scale integration (LSI) technology (also known as system-on-a-chip (SoC) technology) and high-speed frontend electronics for optical access systems being conducted at NTT Microsystem Integration Laboratories. This article provides an overview and the other articles discuss their roles and characteristics well as related design technology and issues.

### 1. Introduction

Opportunities to use a variety of applications on the Internet in daily life are increasing, and Internet access is becoming indispensable. It is desirable for high-quality, convenient, and safe application services to become even more common. This is backed up by the existence of a secure, broadband network services infrastructure utilizing the low losses of optical fiber and the broad bandwidth of light, so networking advances should contribute to a more vibrant, rich, and plentiful society. Optical networks have various components, each playing an important role, including (1) optical devices such as light sources, modulators, transmitters, splitters, and multiplexers; (2) electrical devices that reproduce and process signals and communications protocol controllers; and (3) software that operates them and the communications systems they are part of. At NTT Microsystem Integration Laboratories, one focus of our work is research and development (R&D) of electronics for these communications systems of these types.

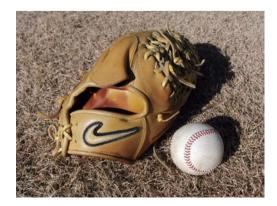

Among electronic device technologies used in telecommunications systems, ones that we view as particularly important include system large-scale integration (system LSI), which is also known as systemon-a-chip (SoC) technology, which provides sophisticated communications functions, and optical frontend integrated circuits (ICs), which perform highspeed signal processing. SoC technology generally refers to implementations that include a central processing unit (CPU), memory, and large-scale dedicated logic, along with the software to operate it (**Fig. 1**). SoC technology is used widely, including in general-purpose and household products, but we focus on applications for communications systems using SoC devices (SoCs) that incorporate our experience and knowledge as a communications carrier and contribute to the advancement of communications

Fig. 1. Elemental SoC architecture.

<sup>†</sup> NTT Microsystem Integration Laboratories Atsugi-shi, 243-0198 Japan

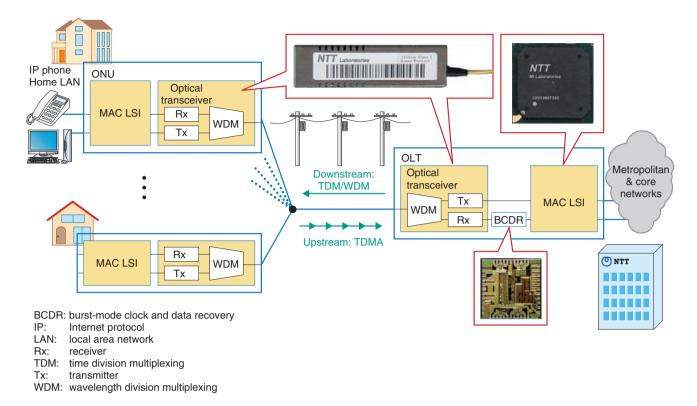

Fig. 2. Electronic devices used in an Ethernet PON system.

systems. We are conducting R&D of SoC design technology, including hardware and some of the software, in cooperation with other research laboratories working in the field of communications systems.

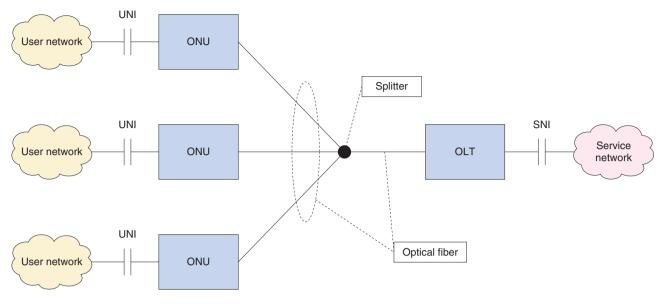

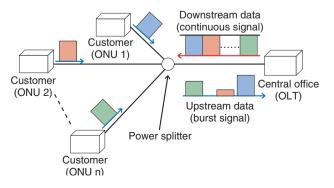

### 2. SoC design for optical access networks

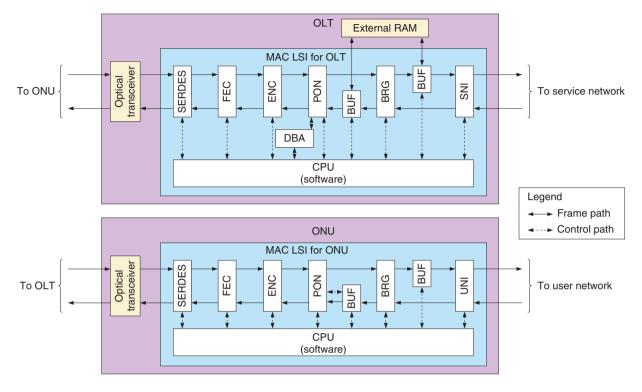

In Japan, most broadband access services are currently provided by fiber-to-the-home (FTTH) access, and they mostly use the GE-PON (Gigabit Ethernet passive optical network) system [1], [2]. A block diagram of an Ethernet PON system is shown in Fig. 2. A PON allows services to be provided to multiple customers economically by branching a single fiber. It requires the formation of a secure and efficient point-to-multipoint (P2MP) connection between the optical line terminal (OLT) on the network side and the optical network units (ONUs) at the customers' locations. This is done by sending upstream signals from ONUs to the OLT by using time-division multiple access (TDMA), which is controlled using the multipoint control protocol (MPCP). The main functional components of the OLT and ONU are media access control (MAC) LSIs, which are SoCs, and optical transceivers. The MPCP processing function is implemented in the MAC LSI. Furthermore, the optical transceiver must be able to amplify and regenerate burst frames sent from multiple ONUs when frames have different timings and optical intensities. The electrical components in this optical transceiver are called the optical front-end ICs. At the beginning of system development, functions that could not be included in the SoC were implemented using external components, but as the technology advanced, more of the functions could be integrated into the SoC, reducing the number of parts and overall cost.

Standardization of 10G-EPON (10-Gbit/s Ethernet PON), the successor to GE-PON, has recently made progress [2]–[4]. We have responded to this by establishing technology for implementing the standard functions of 10G-EPON in SoCs and optical frontend ICs. We have also conducted feasibility studies on achieving more-sophisticated and higher-performance devices. Below, we discuss the characteristics and technical directions for SoCs and optical frontend ICs in the context of Ethernet PON systems.

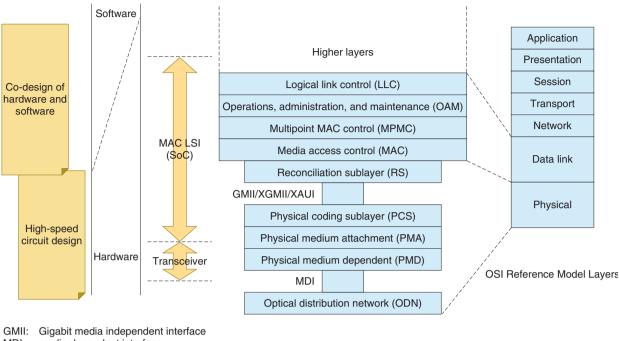

MDI: media dependant interface

OSI: open systems interconnection

XAUI: 10 Gigabit attachment unit interface

XGMII: 10 Gigabit media independent interface

Fig. 3. Architectural positioning of P2MP topologies in the IEEE 802.3ah "Ethernet in the First Mile" and their implementation by the transceiver and the MAC LSI.

### 3. Cooperative design of hardware and software

When one is implementing the required functions in an SoC, a major issue is to develop design methods that optimize the partitioning of functionality between functions implemented in hardware with dedicated logic and functions handled by the CPU using software and to generate interfaces between them.

For communications operators like NTT, a major concern is whether the systems being developed are flexible enough to accommodate extensions for future services, maintenance, and monitoring functions. Up until now, the general approach to implementing these types of flexible functionality in SoCs has been to use software, but if cooperative design of hardware and software were easier, then circuit configuration and control could be done in more detail, allowing one to pursue both extensibility and flexibility.

Moreover, a basic performance requirement for OLTs, ONUs, and, in general, network switches is the capability to process signals at *wire speed*. To handle the requirements of increased traffic, transmission

capacity must be expanded and data must be processed without any frame loss, which places a demand for increased performance on SoCs. To achieve this high performance, hardware techniques for increasing speed play an important role, such as using faster algorithms for logic circuits, parallelization, and pipelining, but we believe that we should also be able to make breakthroughs in power saving for the overall system through better cooperation between hardware and software and by controlling hardware according to actual traffic conditions.

### 4. MAC LSI functionality

The P2MP architecture [5] specified in IEEE802.3ah, the standard for Ethernet PON systems, and the way in which the architecture is implemented using MAC LSIs, transceivers, and other components are shown in **Fig. 3**. Most of the functions required by the system are implemented in the MAC LSI. Most of the functions required by the system are integrated on a single chip, focusing on the various Layer 2 switch (data-link layer) functions from higher-ranking functions such as encryption to physical-layer functions such as encoding and serial/parallel conversion.

### 5. Research on optical front-end ICs

NTT Microsystem Integration Laboratories, together with the NTT Photonics Laboratories, is continually advancing R&D of optical front-end technology. Optical front-end ICs, include amplifiers that reshape in the receiver the weak signals attenuated by transmission through the fiber, digital-data retiming and regeneration circuits, and laser-driver circuits required to produce good quality signals in the transmitter. In the system, these are sections with strict analog requirements, such as sensitivity, feedback or feedforward control, and dynamic range; moreover, they require broadband operation. Furthermore, there is the additional difficulty, mentioned earlier, that data frames arrive at the OLT in burst mode in the PON system. Research issues for these circuits are more physical compared with large-scale SoCs, involving transistor-level circuit design, as well as the physical layout of the circuit and packaging. The selection of semiconductor technology is also an important factor in satisfying performance requirements. We consider (1) compound semiconductors such as InP for heterojunction bipolar transistors (HBTs) and high electron mobility transistors (HEMTs) and GaAs for metal semiconductor field effect transistors (MESFETs), (2) silicon bipolarjunction transistors integrated with complementary metal-oxide semiconductor (CMOS) transistors on a single substrate (Si BiCMOS) including silicon-germanium BiCMOS (SiGe BiCMOS), which integrates SiGe HBTs with conventional CMOS processing, and (3) silicon CMOS (Si CMOS) from cost and performance perspectives and select the optimal technology for a given application.

In R&D of optical front-end ICs, there are two key points to consider. First, as with other long-term basic research, it is important to ascertain the feasibility of the technology. When planning and developing innovative services or systems, one must verify in advance whether they are achievable. For example, in order to progress from GE-PON to 10G-EPON, which is a ten-fold increase in transmission capacity, it is necessary to make front-end ICs that are ten times as fast at handling received frames. In particular, the frame header synchronization speed has a great effect on system design with respect to transmission efficiency. Moreover, sensitivity can have an effect on transmis-

Y in burst for these rrge-scale esign, as d packagnology is This topic has five Feature Articles, including this one which discussed our initiatives related to SoC technology for optical access communications systems and optical front-end IC technology. Next, "Cooperative Hardware/software Design Technolo-

R&D.

"Cooperative Hardware/software Design Technology" [6] describes a high-level design technology using virtual hardware effectively for the initial stages of design, including cooperative design. "MAC LSI Design Technology for Optical Access Communications" [7] explains the LSI design process flow and discusses the architecture of an Ethernet PON SoC in detail. "Design Verification Using Field-programmable Gate Arrays for Optical Access Communications SoC" [8] introduces a technology for verifying largescale SoC functions using field programmable gate arrays before chip prototypes are created. Finally, "10-Gbit/s Burst-mode Receiver Integrated Circuits for Broadband Optical Access Networks" [9] introduces the state of development of optical front-end IC technology for 10G-EPON systems.

sion distance or the number of customers that can be

accommodated in a single optical distribution net-

work. In this way, the performance levels achievable in the front end have a large effect on overall system

specifications, so basic research in this area is done as a precursor to standardization. By conducting R&D

in the area that is the physical bottleneck for perfor-

mance, we will be able to contribute to higher system

The second point is that there is synergy in having

both SoC technology and front-end technology. Having experience with both makes it easier to study

overall optimizations such as controlling the front

end from the SoC or optimizing the chip partitioning

and interface implementations. We want to use this

synergy as one of our strengths in proceeding with

6. Organization of the Feature Articles

performance and lead the industry.

### 7. Future trends

At NTT Laboratories, we will continue to expand our R&D efforts toward improving the value provided to customers and resolving business issues. To do so, we will continue development of SoC technology in order to further increase system performance, pursue "Green of ICT" much further, and contribute to making systems more flexible by improving customizability and other aspects (ICT: information and communications technology). Until now, the integration level of LSIs has increased according to Moore's Law\* year after year, and this has been the force behind progress in the functionality and performance of semiconductor products. At the beginning of this century, there was some serious discussion about reaching practical limits for reductions in the size of semiconductor processes, but now it appears that some of the fabrication process problems will be solved, and the International Technology Roadmap for Semiconductors (ITRS) [10] has continued to issue roadmaps for still finer technologies. Accordingly, there is hope for continued progress in SoCs and communications systems through R&D driven by leading-edge processes.

On the other hand, in addition to active R&D on further miniaturization (*more Moore*), new functional materials and devices are being developed, in synergy with miniaturization (*more than Moore*), and research on utilizing more-than-Moore technology for communications systems in the medium-to-long term will also be important.

\* Moore's Law: A law that states that the density of semiconductor integration will double every 18 to 24 months.

### References

Technical Fundamentals Lecture: "GE-PON Technology, No. 1 to No. 5," NTT Technical Journal, Vol. 17, No. 8–12, 2005 (in Japanese).

#### Tsugumichi Shibata

Executive Manager, Ubiquitous Interface Laboratory, Project Manager, First Promotion Project, NTT Microsystem Integration Laboratories.

He graduated from Tokyo National College of Technology in 1980 and received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Tokyo in 1983, 1985, and 1995, respectively. In 1985, he joined NTT, where he engaged in research on electromagnetic-field analyses and high-speed ICs for data transmission systems. From 1996 to 1997, he was a Visiting Scholar at the University of California at Los Angeles (UCLA), where he did research on diakoptics in numerical simulation. He was the chair of the Microwave Simulator Technical Group of the Institute of Electronics. Information and Communication Engineers (IEICE) from 2003 to 2005 and a vice president of the IEICE Electronics Society from 2007 to 2009. He has been serving as an Executive Committee member of the VLSI Symposia since 2007 and is also an Executive Committee member of the 2010 APMC. He is a senior member of IEEE and IEICE.

http://www.ntt.co.jp/journal/0508/files/jn200508071.pdf http://www.ntt.co.jp/journal/0509/files/jn200509091.pdf http://www.ntt.co.jp/journal/0510/files/jn200510067.pdf http://www.ntt.co.jp/journal/0511/files/jn200511059.pdf http://www.ntt.co.jp/journal/0512/files/jn200512051.pdf

- [2] K. Kumozaki, "Optical Access Systems: Present State and Future Directions," NTT Technical Review, Vol. 6, No. 5, 2008. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2008 05sf2.html

- [3] M. Tsubokawa, "Optical Access Network System Technologies," IEICE Journal, Vol. 91, No. 8, pp. 699–705, 2008 (in Japanese).

- [4] J. Kani and K. Suzuki, "Standardization Trends of Next-generation 10 Gigabit-class Passive Optical Network Systems," NTT Technical Review, Vol. 7, No. 11, 2009. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2009 11gls.html

- [5] www.ieee802.org/3/index.html

- [6] T. Aoki, T. Ohtsuka, K. Yamazaki, S. Onishi, and A. Onozawa, "Cooperative Hardware/software Design Technology," NTT Technical Review, Vol. 9, No. 3, 2011. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa2.html

- [7] A. Miyazaki, M. Urano, H. Suto, and K. Terada, "MAC LSI Design Technology for Optical Access Communications," NTT Technical Review, Vol. 9, No. 3, 2011. https://www.etu-accession/cachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attrachiva/attr

https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa3.html

[8] R. Kusaba, S. Yasuda, K. Kawai, T. Kawamura, and S. Oteru, "Design Verification Using Field-programmable Gate Arrays for Optical Access Communications SoC," NTT Technical Review, Vol. 9, No. 3, 2011.

https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa4.html

[9] M. Nogawa, H. Katsurai, M. Nakamura, H. Kamitsuna, and Y. Ohtomo, "10-Gbit/s Burst-mode Receiver Integrated Circuits for Broadband Optical Access Networks," NTT Technical Review, Vol. 9, No. 3, 2011.

https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa5.html

[10] www.itrs.net/

### Mamoru Nakanishi

Senior Research Engineer, Supervisor, First Promotion Project, NTT Microsystem Integration Laboratories.

He received the B.E. and M.E. degrees in physical electronics from Tokyo Institute of Technology in 1986 and 1988, respectively. He joined NTT LSI Laboratories in 1988. He has been engaged in research on highly parallel architectures and their applications for image processing. He is currently engaged in SoC development for the access networks. He is a member of IEICE, the Information Processing Society of Japan, and the IEEE Computer Societv.

### Mamoru Kitamura

Director, NTT Microsystem Integration Laboratories.

He received the B.S., M.S., and Ph.D. degrees from the University of Tokyo in 1980, 1982, and 1985, respectively. He joined NTT Electrical Communications Laboratories, Atsugi, Kanagawa, in 1985, where he engaged in the development of LSI fabrication processes and devices for telecommunication use. His research activities also include access network systems and video communication systems.

# **Cooperative Hardware/software Design Technology**

### Takashi Aoki<sup>†</sup>, Takuya Ohtsuka, Koji Yamazaki, Shigehiko Onishi, and Akira Onozawa

### Abstract

In this article, we introduce a hardware/software co-design simulation method for testing the cooperative design of hardware and software for system-on-a-chip (SoC) devices. For SoCs, which incorporate dedicated processing circuits and a processor, combined testing of the software running on the processor and the operations of the dedicated circuits must be done from the initial design stages in order to reduce the amount of redesign and the turnaround time, i.e., the number of person-hours of work required. Our cooperative simulation method uses virtual hardware. We discuss its effectiveness by referring to real examples.

### 1. Introduction

In the design of system-on-a-chip (SoC) devices, it is extremely important to design so that the hardware, which handles specialized processing, and the software running on the microprocessor, operate cooperatively. In other words, the design process must also be cooperative. How can this be tested?

The microprocessor operates according to what is written in its program (software). On the other hand, the dedicated processing circuits process data continuously according to how the hardware has been designed and a clock signal. Thus, the operation of the two must be checked to ensure that they do not cause a conflict, mismatch, deadlock, or other type of performance drop. This is cooperative design evaluation.

The evaluation results can affect the system architecture greatly, so such an evaluation must be done from the initial stages and from the top level of design. However, at the top-level design stage, there is no actual hardware. It would be nice to build an overall prototype including both the microprocessor and dedicated circuits, put them together and test them, but development usually cannot wait for this. Systems being implemented as SoCs have recently become extremely complex, so that even building or rebuilding a single prototype can take several weeks or months. For this reason, it has become necessary to simulate the hardware together with the system software before prototyping it; in other words, one must perform a hardware/software co-design simulation.

### 2. Virtual hardware

To implement co-design simulation, we need a simulator for virtual hardware. Physical hardware operates with a clock signal for input and output to the dedicated circuits so the processor can read from and write to it, but virtual hardware does not have a physical clock. Instead, attention must be paid to the sequencing and dependencies of reading and writing and to the input and output between the processor and dedicated circuits, and the simulator must be built to maintain these relationships.

Before the design of the dedicated circuits is complete, one does not know how many clock cycles will be required for these circuits to complete their operation. However, the correct sequencing and dependencies for reading and writing are correctly coded in the virtual hardware, so the virtual hardware can respond to the software behavior without conflict. This makes co-design simulation possible from the top-level design stages.

<sup>†</sup> NTT Microsystem Integration Laboratories Atsugi-shi, 243-0198 Japan

Cooperative hardware/software design

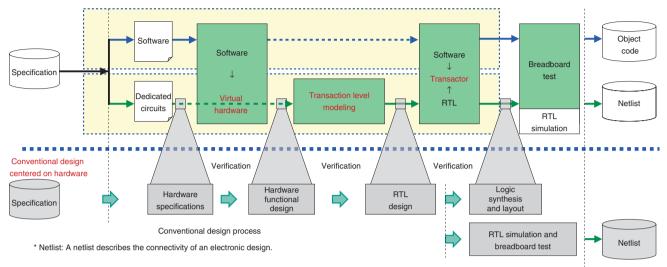

Fig. 1. New design process that allows cooperative testing with software.

### 3. Issues being addressed

We have applied this type of co-design simulation using virtual hardware to the evaluation of SoC designs for optical access systems. As a result, we have confirmed the usefulness of the method. The new process is shown in Fig. 1 together with the conventional design process. The lower half of the figure shows the conventional design process centered on hardware. Here, the hardware was the only specification to achieve. However, in hardware/software codesign, which allows cooperative testing with the software, part of the specification is achieved with software. The hardware/software co-design process can handle a wider specification range than the conventional design process. Moreover, whereas the conventional design process creates a hardware netlist, the cooperative design process creates two netlists-one for the dedicated circuits and another that connects the processor and dedicated circuitsand software object code that controls the processor's behavior. Therefore, Specification and Netlist are grayed out in the lower half of Fig. 1 because they cover different ranges to those in the upper half.

The dedicated circuits are designed according to the conventional hardware design process: they become more detailed in three stages from specifications to functional design and register transfer level (RTL) design. Software cooperative testing (verification) can be done at each of these three stages by using co-design simulation with virtual hardware.

We started by building the virtual hardware (leftmost green box in Fig. 1.) for the initial stage (specification design). This allowed early verification of the SoC software.

Then, at the intermediate stage (functional design), we addressed the hardware transaction-level design (second green box). This can be simulated several times faster than when designing in detail to the RTL level.

Finally, at the RTL design stage, we built a mechanism called a transactor (third green box) into the system for sections connecting the dedicated circuits with the processor. This enables precise final verification of the interfaces between hardware and software in the SoC.

### 4. Construction of virtual hardware

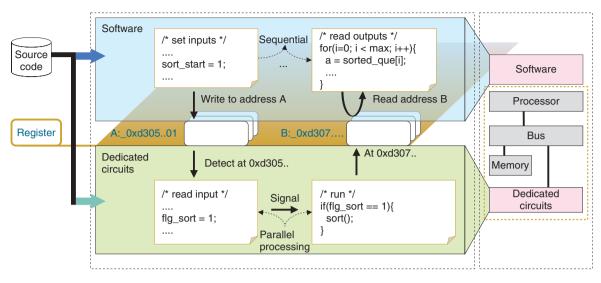

We verify the software at the specification design stage with the goal of determining aspects such as whether adequate performance is achieved and whether performance will drop owing to interference with the dedicated circuits. The software is not executed independently, but loaded on the original SoC architecture, which includes both the processor and dedicated circuits. Thus, we have built virtual hardware that simulates the entire SoC, as shown in **Fig. 2**.

The key to building virtual hardware is the separate

\* http://www.synopsys.com/Community/Interoperability/SystemLevelCatalyst/Pages/MVaST.aspx

parts for software and dedicated circuits, which are where the processing that defines the functional characteristics of the SoC takes place. For our opticalaccess SoC, these characteristics were the ability to interface with sophisticated, high-speed communication lines. The specifications for these components are complex, so they were expressed not only in documents, but also as source code in the C programming language. To ensure that the implementation was faithful to the specifications, we built the dedicated circuit part of the virtual hardware by directly using this C source code as far as possible.

The source code includes both the software that will be loaded by the processor in the SoC and the software representing the dedicated circuits. Communication between them uses registers, which create the correspondence between variables in the software and variables for the dedicated circuits, so the address-mappings for these registers must be managed. The mechanism of communication between software and a dedicated circuit conducted via a register is shown in Fig. 2. When the software side writes to address A, the dedicated circuit side detects it as being written at address 0xd305... (in hexadecimal). Because the dedicated circuit is always processing, the influence of the write will sooner or later be written at address 0xd307..., which is equivalent to Address B on the software side. The software side reads values from Address B according to the execution order and conditional judgment. The dedicated circuit reads the value that was written earlier to Address B, and, as a result of the dedicated circuit procedure, its behavior when it reads Address B reflects the software side.

The number of these registers is generally very large. Most of the specification is related to these registers, so any updates to the specifications can involve a significant amount of rewriting in the virtual hardware. This results in additional design work, so we used data structures, which allow us to manage all of the registers at once and make it easy to apply updates to the specification.

This approach can be generalized, decreasing the amount of time required from confirmation of the specifications to system-level operation. For the current project, we were able to detect routines that were performing inadequately several months before beginning verification of the physical hardware.

### 5. Transaction-level design

In the same way that software performance can be checked using virtual hardware, the dedicated circuits can be simulated at the functional design stage. This simulation is faster than RTL-stage simulation, but it must be done using transaction level modeling (TLM) to describe the transaction-level design.

In the past, for functional design simulations, each of the lines between modules would be simulated individually and in complete detail, down to individual

Fig. 2. Virtual hardware.

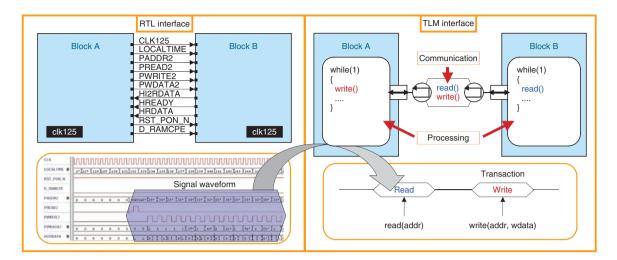

Fig. 3. TLM interface.

clock cycles. This resulted in a number of problems. First, a lot of work was required to complete the detailed design before simulation could begin; moreover, component redesign because of interference with other blocks could have a major effect on the design schedule [1]. Second, a detailed simulation could not be executed quickly and consumed much time. Third, the test coverage was difficult to manage [2].

To resolve these difficulties, we used SystemC [3] TLM to structure the design file for the dedicated circuit section. At the functional design stage, testing must verify points where data is exchanged between blocks. The TLM interface between blocks A and B is compared with the RTL interface in Fig. 3. When a block passes the results of its processing to another block, the procedure can be very long, as in the RTL case on the left. However, this procedure can become very simple, as shown on the right side, if the exchange is rewritten as a transaction. A transaction is the core action, such as the start or confirmation of a transmission or reception. The events handled in a simulation using TLM are arranged beforehand, so simulation can be done at high speed. When TLM is used, descriptors for the lines connecting blocks are much shorter, and this effectively reduces the amount of preparation work for simulation. Overall, the amount of descriptor code was about one-tenth of that for RTL, and the simulation executed about 100 times as fast as the RTL simulation.

### 6. Built-in transactors

Completing an RTL design of the dedicated-circuit section enables precise simulations to be done in block units, but problems arise when cooperative simulation is performed. The processor in the virtual hardware does not have actual signal lines, so the RTL for the dedicated circuit section cannot be connected to the virtual hardware as it is.

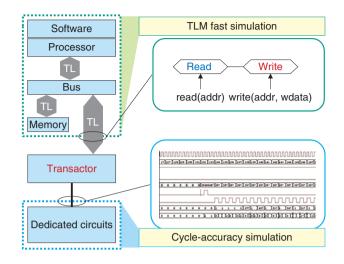

Thus, we built transactors into the virtual hardware, as shown in Fig. 4. Transactors are composed of libraries provided by the existing simulation infrastructure [4]. We used library functions to code the transactor to monitor accesses to the bus by the RTL of the dedicated circuits. When an access is detected, a function updates the register value at the appropriate address. Figure 4 shows a transactor connecting two simulators: the lower one simulates the dedicated circuits with cycle accuracy and the upper one simulates the software-equipped processor with fast TLM. The grey areas labeled TL (transaction level) mean that a TL connection is used when these areas are simulated. In the processor and bus in this area, when each part performs communications with the other part, the performance is set using a TL write. The TL connection enables communications to be performed with transaction between connected parts (models) and leads to high-speed simulation. On the other hand, the area of dedicated circuits is written to enable simulation with more detailed cycle accuracy. There is no way to connect directly between an area that uses TL connection when simulated and another

TL: transaction level

Fig. 4. Built-in transactors.

area simulated with cycle accuracy because the input/ output signal formats are completely different. That is why a transactor plays the role of a mutual conversion function for the two communication methods.

With the earlier approach, we built a prototype board, reproduced the RTL on a field-programmable gate array (FPGA), and loaded the software onto the processor to evaluate the whole system. The data for writing the FPGA was created using computer-aided design, and this also required several weeks of preparatory work. In comparison, using the new method, the design for this project required only five persondays of preparation before evaluation was started. The method cannot replace all of the testing done with a prototype board, such as realtime signal processing, but final testing can be started several weeks earlier; the saved time is the time that would have been required to prepare the data for rewriting the board.

### 7. Cooperative design technology in the future

In this article, we introduced an example of applying cooperative design methods to the design of an SoC for optical access. Through this example, we showed that system-level cooperative simulation, at a level of precision appropriate and relevant for design stages as they progress, is possible for the dedicated circuit components, from top-level design to the final processes.

In the future, it will become more important to do multistage cooperative simulation, from the beginning and in accordance with the design stages, when designing SoCs. The future possibilities enabled by this sort of design methodology are not limited to SoCs. Large-scale systems of even more complexity will fall into the scope of this research and we are taking on this new challenge.

### References

[1] CoMET.

http://www.synopsys.com/Systems/VirtualPrototyping/Pages/VP-Tools.aspx

- [2] K. Yamazaki, T. Aoki, I. Harada, and A. Onozawa, "High-level Verification Environments Using Redundant Pattern Compression Methods," IEICE Conf. Proc., Vol. 2009, p. 53 (in Japanese).

- [3] OSCI (Open SystemC Initiative). http://www.systemc.org/home/

- [4] Carbon SoC Designer (in Japanese). http://www.carbondesignsystems.co.jp/products\_socd.asp

### Takashi Aoki

Research Engineer, Design Technology Research Group, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories. He received the B.S. and M.S. degrees in applied physics from Tokyo Institute of Technology in 1987 and 1989, respectively. He joined NTT in 1989 and studied LSI design and network design. He is a member of the Information Processing Society of Japan (IPSJ) and the Physical Society of Japan.

### Shigehiko Onishi

Research Engineer, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories.

He received the B.E. and M.E. degrees from Yokohama National University, Kanagawa, in 1991 and 1993, respectively. He joined NTT in 1993. Since then, he has been working on R&D of LSIs, speech recognition, video coding, and high-performance computing. He is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) and the Acoustical Society of Japan.

#### Takuya Ohtsuka

Research Engineer, Design Technology Research Group, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories. He received the B.E. and M.E. degrees in science and engineering from Waseda University, Tokyo, in 1997 and 1999, respectively. He joined NTT in 1999.

#### Akira Onozawa

Senior Research Engineer, Supervisor, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories.

He received the B.E. and M.E. degrees in electronic communication engineering and the Ph.D. degree in information science all from Waseda University, Tokyo, in 1983, 1985, and 2002, respectively. He joined NTT in 1985. Since then, he has been working on R&D of LSIs and related CAD systems. He is a member of the Association of Computing Machinery, IEEE, IEICE, and IPSJ.

#### Koji Yamazaki

Research Engineer, Design Technology Research Group, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories.

He received the B.S. degree in environmental information science from Keio University, Kanagawa, and the M.S. degree in interdisciplinary information science from the University of Tokyo in 2000 and 2004, respectively. He joined NTT in 2004. Since then, he has been working on R&D of LSIs and related CAD systems. He is a member of IPSJ.

# MAC LSI Design Technology for Optical Access Communications

### Akihiko Miyazaki<sup>†</sup>, Masami Urano, Hiroki Suto, and Kazuhiko Terada

### Abstract

In this article, we explain the development process and architecture of a media access control (MAC) large-scale integrated circuit (LSI). The MAC LSI is a very important component that provides most of the functions of an optical line terminal and optical network unit, which are the main devices in an optical access system. The required functions include the passive optical network interface, buffers, bridges, and maintenance & authentication.

### 1. Introduction

The development of a large-scale integrated circuit (LSI) begins with the definition of requirements. For this, the specifications of the systems in which the LSI will be used must first be decided appropriately. A media access control (MAC) LSI is a very important component in an optical access system because these LSIs provide most of the functions of the optical line terminals (OLTs) and optical network units (ONUs), which are the main devices. The MAC LSI is classified as a system on a chip (SoC) because it contains a central processing unit (CPU), memory, and large-scale dedicated logic circuits. When MAC LSI development begins, many details of the service and system specifications are still undecided, so while the specifications are being decided, close communication must be kept with internal departments studying the next-generation systems. For each system function, one must decide whether it will be implemented in the LSI or by using external components. As many functions as possible should be placed in the LSI to reduce the number of external parts and hence the equipment cost. However, as the number of functions in the LSI increases, the cost of the LSI itself also increases, so a good balance must be found.

Requirements other than functionality must also be decided appropriately, including power consumption targets or performance parameters such as frame processing speed and processing time.

### 2. LSI design

After the LSI requirements have been decided, one must decide which of the functions are to be implemented in hardware and which in software. Generally, functions that require high performance are implemented in hardware, and ones that require a flexible configuration are done in software. For a MAC LSI, functionality must be allocated to satisfy the requirement that all input frames can be processed, without the speed dropping below the wire speed.

Once the hardware/software assignments have been decided, their designs can proceed. We try to keep the hardware design as small as possible while meeting the performance requirements, but we must also consider the following points:

- (1) Each function should be able to be modified flexibly through configuration. This is so that, for example, if standards have not been finalized at the development stage, they can be accommodated even if they do change without the hardware needing to be rebuilt.

- (2) At the beginning of development, in particular, in addition to the functions required for services, testing and debugging functions needed during

<sup>†</sup> NTT Microsystem Integration Laboratories Atsugi-shi, 243-0198 Japan

development should also be provided. Examples of functions of this sort are a loopback for the main signal, various counters, and internal signal monitoring functions.

The software can be categorized into components that access the hardware and those that do not, and the software design can proceed more smoothly if the hardware-accessing components are designed as application programming interfaces.

### 3. Coding and verification

The next part of the design is coding. For the hardware, we use a register transfer level (RTL) description with a hardware description language such as Verilog-HDL. For the software, we mainly use the C language.

Coding is followed by verification testing. Once the hardware has been built, making further changes is extremely expensive and time consuming, so testing must be done before production to eliminate as many problems as possible.

For the hardware, in addition to using logical simulation to check operations, we check some of the functions by actually running them using field programmable gate arrays (FPGAs) to emulate the hardware. Verification using FPGAs is discussed in detail in the fourth Feature Article in this issue, "Design Verification Using Field-programmable Gate Arrays for Optical Access Communications SoC" [1].

The operation of the software must ultimately be checked on the actual hardware, but as hardware and software development proceeds in parallel, the software must be tested as far as possible before the hardware is complete. For this purpose, a software model simulating the hardware is created. This is discussed in detail in the second Feature Article in this issue, "Cooperative Hardware/software Design Technology" [2].

When testing is complete, a logic-synthesis tool is used to create a netlist\* from the RTL description. Once the RTL description has passed all testing, it is called the *clean file*, and a netlist created from this clean RTL description is passed to an LSI manufacturer for outsourced production.

### 4. MAC LSI architecture

Having given a step-by-step explanation of the LSI development process above, we now describe the architecture of the optical access communications MAC LSI.

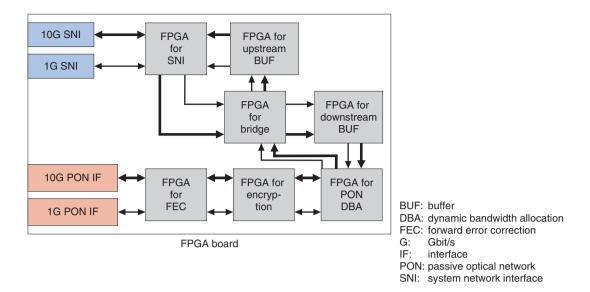

There are several optical access methods, but as an example, we describe EPON (Ethernet passive optical network) here. There are two types of EPON [4], [5]: GE-PON (Gigabit Ethernet passive optical network) with a frame rate of 1 Gbit/s and 10G-EPON at 10 Gbit/s, but most of the following description applies to both equally. An overview of the EPON system is shown in **Fig. 1**. It is composed of an OLT, ONUs, optical fibers, and splitters. The OLT, which is usually in the provider's central office, is connected to the service network through the service node interface (SNI), and an ONU, which is usually on the user's premises, is connected to the user network through the user network interface (UNI).

The functions required by the OLT and ONU, with explanations, are given in **Table 1**. Each of these functions must be implemented either in the LSI or by using external components. For LSI implementation, each function is designed in a cluster called a functional block. The correspondence between functional blocks and these functions is shown in Table 1. The functional blocks are divided into two types: (1) functional blocks that receive, process, and transmit frames and (2) other functional blocks.

In Table 1, the dynamic bandwidth allocation (DBA) and CPU sections are of type (2) and the rest are of type (1). The MAC LSI architecture can be formed by arranging the type (1) functional blocks in the order of frame flow, and connecting type (2) blocks to the blocks that they control. Examples of OLT and ONU implementations using an LSI with this architecture are shown in **Fig. 2**. As shown clearly in Table 1 and Fig. 2, most of the functions of both OLT and ONU are implemented in the MAC LSI.

The MAC LSIs for the OLT and ONU in Fig. 2 have similar structures, but although they may share the same name for a functional block, there are differences in the functional blocks of the OLT and ONU, as described below.

- (1) Within the EPON system, multiple ONUs connect to a single OLT, so all blocks except the SERDES (serializer/deserializer), SNI, and CPU in the OLT MAC LSI must be able to handle multiple ONUs.

- (2) To implement the PON control function, the PON components of the MAC LSI for OLT and ONU must each transmit and receive control frames according to the well-defined sequence for each. The PON control function is described

Netlist: A netlist describes the connectivity of an electronic design [3].

Fig. 1. Outline of EPON system.

| Function              |                        | Description                                                                                             | Functional block implementing the function    |                      |

|-----------------------|------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------|

|                       |                        |                                                                                                         | OLT                                           | ONU                  |

| PON<br>interface*     | Optical<br>transceiver | Converts optical signal to electric signal and vice versa.                                              | (external component)                          | (external component) |

|                       | SERDES                 | Converts serial signal to parallel signal and vice versa.                                               | SERDES                                        | SERDES               |

|                       | PCS                    | Channel coding and error correction                                                                     | FEC                                           | FEC                  |

|                       | PON control            | Transmits and receives MPCP frames, maintains logical link, and adjusts local time for synchronization. | PON, CPU<br>(software)                        | PON                  |

| DBA                   |                        | Allocates bandwidth for upstream transmission.                                                          | DBA                                           | (not applicable)     |

| Encryption/decryption |                        | Performs encryption and decryption.                                                                     | ENC                                           | ENC                  |

| Buffer                |                        | Temporarily buffers frames and counts accumulated frames (only in ONU).                                 | BUF,<br>external RAM                          | BUF                  |

| Bridge                |                        | Bridges between service network and PON (in OLT).<br>Bridges between user network and PON (in ONU).     | BRG                                           | BRG                  |

| VLAN                  |                        | Frame processing based on VLAN tags                                                                     |                                               |                      |

| Priority control      |                        | Priority queuing of the frames                                                                          |                                               |                      |

| SNI                   |                        | Interface between service network and OLT                                                               | SNI                                           | (not applicable)     |

| UNI                   |                        | Interface between user network and ONU                                                                  | (not applicable)                              | UNI                  |

| Maintenance*          |                        | Transmits and receives OAM frames.                                                                      | smits and receives OAM frames. CPU (software) |                      |

| Authentication        |                        | Authenticates ONUs. CPU (so                                                                             |                                               | CPU (software)       |

| Table 1. | Functions of OLT | and ONU | and functional | blocks in MAC LSI. |

|----------|------------------|---------|----------------|--------------------|

|----------|------------------|---------|----------------|--------------------|

\* IEEE802.3/IEEE802.3av compliant

| BRG: bridge                   |

|-------------------------------|

| ENC: encryption               |

| FEC: forward error correction |

OAM: operations, administration, and maintenance PCS: physical coding sublayer RAM: random access memory VLAN: virtual local area network

Fig. 2. Examples of MAC LSI block diagrams (top: OLT, bottom: ONU).

later.

- (3) Uplink bandwidth allocation is required only in the OLT, so only the OLT has the DBA block. Conversely, the ONU must notify the OLT of accumulated frames, so the accumulated frame calculation function is present only in the buffer (BUF) section of the ONU.

- (4) In the PON section for EPON, the downlink is a continuous signal, but the uplink is a burst-mode signal, so the ONU transmitter and the OLT receiver must support burst-mode communication. Burst-mode communication is described in detail in the fifth Feature Article "10-Gbit/s Burst-mode Receiver Integrated Circuits for Broadband Optical Access Networks" [5].

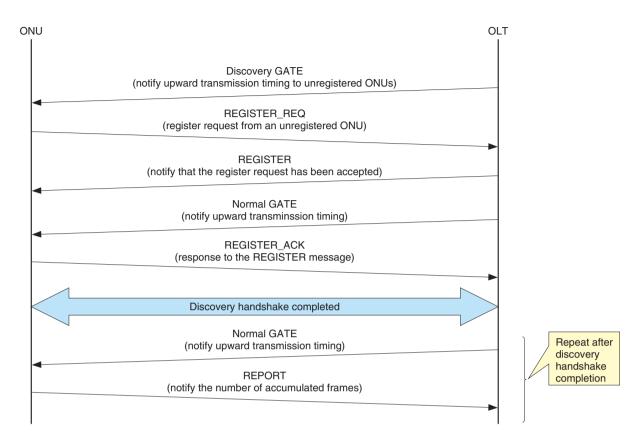

### 5. PON control function

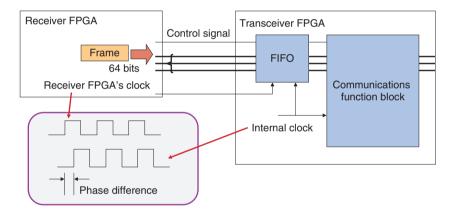

The PON control function is an important function that administers the OLT-ONU links. When a new ONU connects to the PON, the PON control functions of the OLT and ONU establish a link by exchanging multipoint control protocol (MPCP) control frames in the sequence shown in **Fig. 3**. The process by which a newly connected ONU establishes a link is called *discovery*. Once discovery has been completed, MPCP control frames are exchanged periodically for link maintenance.

EPON uses time-division multiple access on the uplink, so the OLT and ONU must be synchronized, and this is also done by the PON control function. With EPON, the OLT internal clock acts as master, and ONUs are notified of the time by the transmit timestamp set in MPCP control frames. ONUs receiving this notification adjust their clocks to match. This can produce some jitter in the ONU clocks, so the ONU's PON control function must be designed not to malfunction owing to clock jitter.

### 6. Example of MAC LSI prototype

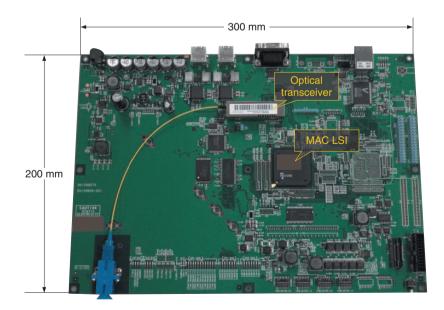

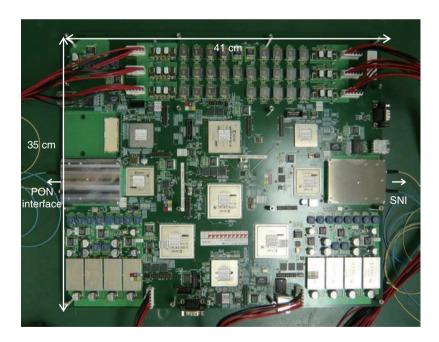

We have built a prototype LSI for a GE-PON ONU as described here. Details of the prototype are given in **Table 2**, and a photograph of the LSI mounted on an evaluation board is shown in **Fig. 4**.

Fig. 3. Discovery handshake message exchange.

Fig. 4. Evaluation board with MAC LSI.

| Logic             | 4.5 M gates       | Total:           |  |

|-------------------|-------------------|------------------|--|

| Memory            | 12.4 Mbit/s       | 90 M transistors |  |

| Die size          | 9.25 mm × 9.25 mm |                  |  |

| Power consumption | 2.2 W             |                  |  |

M: million

### 7. Conclusions and future developments

We described the development process and architecture for a MAC LSI for optical access communications and introduced a prototype of the LSI. 1-Gbit/s services using the GE-PON optical access system have been commercialized. However, the 10-Gbit/s rate for 10G-EPON has already been standardized. and even faster systems are expected in the future. LSI operation speeds are expected to increase slowly in comparison with these data transmission rates, so new architectures may be needed to handle the rising network speeds. Equipment cost reduction and power consumption control will also continue to increase in importance, so technical development be needed for their achievement. Finally, as functionality becomes more complex, the scale of LSIs needed for network-

### Akihiko Miyazaki

Senior Research Engineer, Supervisor, Ubiqui-tous Interface Laboratory, NTT Microsystem Integration Laboratories.

He received the B.S. and M.S. degrees in pure and applied sciences from the University of Tokyo in 1991 and 1993, respectively. In 1993, he joined NTT LSI Laboratories, where he initially engaged in R&D of layout CAD algorithms and systems. In 2000, he moved to NTT Communications and worked on developing application-platform services for enterprise customers. In 2004, he moved to NTT Microsystem Integration Laboratories and is currently working on developing LSIs for optical access communications. He is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) and the Physical Society of Japan

#### Masami Urano

Senior Research Engineer, Supervisor, Ubiqui-tous Interface Laboratory, NTT Microsystem Integration Laboratories.

He received the B.E. and M.E. degrees in electrical and electronics engineering from Sophia University, Tokyo, in 1984 and 1986, respectively. In 1986, he joined NTT Atsugi Electrical Communications Laboratories, where he initially engaged in R&D of the circuit and layout design technology of semi-custom logic LSIs. Since 2005, he has been engaged in R&D of the circuit design technology of Optical Access Communication LSIs. He is a member of IEICE.

ing will continue to increase, so design technology and tools to handle larger-scale LSIs will also need to be developed.

### References

R. Kusaba, S. Yasuda, K. Kawai, T. Kawamura, and S. Oteru, "Design [1] Verification Using Field-programmable Gate Arrays for Optical Access Communications SoC," NTT Technical Review, Vol. 9, No. 3, 2011. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011

03fa4.html

- [2] T. Aoki, T. Ohtsuka, K. Yamazaki, S. Onishi, and A. Onozawa, "Cooperative Hardware/software Design Technology," NTT Technical Review, Vol. 9, No. 3, 2011. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa2.html

- [3] Netlist. http://en.wikipedia.org/wiki/Netlist

- Technical Fundamentals Lecture: "GE-PON Technology, No. 1 to No. [4] 5," NTT Technical Journal, Vol. 17, No. 8-12, 2005 (in Japanese). http://www.ntt.co.jp/journal/0508/files/jn200508071.pdf http://www.ntt.co.jp/journal/0509/files/jn200509091.pdf http://www.ntt.co.jp/journal/0510/files/jn200510067.pdf http://www.ntt.co.jp/journal/0511/files/jn200511059.pdf http://www.ntt.co.jp/journal/0512/files/jn200512051.pdf

- K. Kumozaki, "Optical Access Systems: Present State and Future [5] Directions," NTT Technical Review, Vol. 6, No. 5, 2008. https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2008 05sf2.html

- [6] M. Nogawa, H. Katsurai, M. Nakamura, H. Kamitsuna, and Y. Ohtomo, "10-Gbit/s Burst-mode Receiver Integrated Circuits for Broadband Optical Access Networks," NTT Technical Review, Vol. 9, No. 3 2011

https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr2011 03fa5.html

### Hiroki Suto

Senior Research Engineer, Ubiquitous Inter-face Laboratory, NTT Microsystem Integration Laboratories.

He received the B.E. and M.E. degrees in applied physics from the University of Tokyo in 1983 and 1985, respectively. He joined NTT Atsugi Electrical Communications Laboratories in 1985. Since then, he has been engaged in R&D of GaAs and Si integrated circuit design for highspeed and broadband applications. He is a member of IEICE.

### Kazuhiko Terada

Senior Research Engineer, Ubiquitous Interface Laboratory, NTT Microsystem Integration Laboratories

He received the B.E. and M.E. degrees in electrical and electronic engineering from Kyoto University in 1997 and 1999, respectively. In 1999, he joined NTT Network Innovation Laboratories, where he engaged in R&D of WAN interfaces based on 1- and 10-Gbit/s Ethernet technologies. He is currently studying powerreduction technologies for next-generation optical access. He is a member of IEICE.

### Feature Articles: System LSI Design for Broadband Optical Access Network Systems

# Design Verification Using Fieldprogrammable Gate Arrays for Optical Access Communications SoC

Ritsku Kusaba<sup>†</sup>, Sadayuki Yasuda, Kenji Kawai, Tomoaki Kawamura, and Shoko Oteru

### Abstract

We describe evaluation technology that uses field-programmable gate arrays (FPGAs) to test a system on a chip (SoC). This should reduce the time taken for testing SoCs used in optical access communications by letting us conduct tests using FPGAs in parallel with conventional testing to reduce the testing time and improve the design quality.

### 1. Introduction

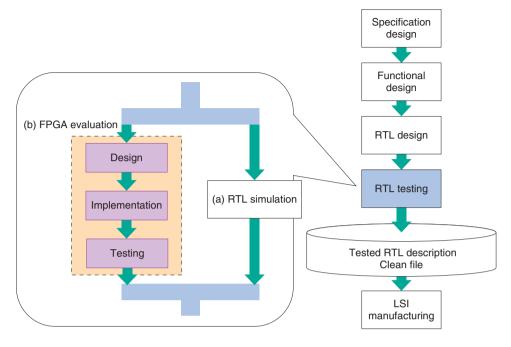

The process of evaluating a system on a chip (SoC) involves verifying a register transfer level (RTL) description. The RTL description is written in a hardware description language and created through specification design, functional design, and RTL design, as shown in the SoC design flow in **Fig. 1**. The result is a verified RTL description, called a *clean file*, which is used next in the large-scale integrated circuit (LSI) production process.

SoC evaluation usually takes several times longer than SoC design, so as the scale of designs increases, the evaluation time is becoming a problem. Moreover, if a problem is discovered during the evaluation, the evaluation process can take even longer because additional checking is needed after the problem has been fixed to ensure that revisions have not affected other aspects of the design. Furthermore, the repair time and cost for fixing problems found after production has begun can be very high, so as much testing as possible must be done to eliminate these problems beforehand.

To date, SoC testing has generally been done using a logic simulator, which is a computer program ((a) in Fig. 1). However, simulating the functions of a largescale device such as an SoC takes a long time, which makes it difficult to test all of the functionality adequately.

### 2. Benefits of FPGA testing

To overcome this problem with logic simulation, it has recently become more common to conduct testing using field-programmable gate arrays (FPGAs) ((b) in Fig. 1) in parallel with logic simulation. An FPGA is an LSI [1] that can be programmed any number of times for the desired logic. In FPGA testing, hardware with the same functionality as the SoC is implemented by writing FPGA design data to an FPGA mounted on an evaluation board. This data is created from the hardware description of the SoC design. The functionality is then checked using measuring instruments to input data and evaluate whether the intended output data is obtained. FPGAs can operate several hundred times faster than a logic simulator, so they make possible long-term, continuous testing that is difficult with simulation.

Functionality can also be evaluated under conditions closer to real ones by connecting the evaluation board to other equipment and communicating at real speeds. FPGA evaluation allows functionality to be tested under more conditions than logic simulation

<sup>†</sup> NTT Microsystem Integration Laboratories Atsugi-shi, 243-0198 Japan

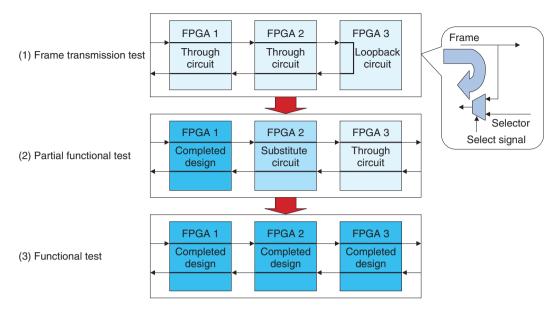

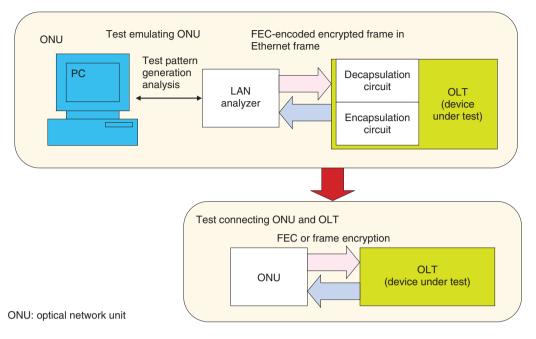

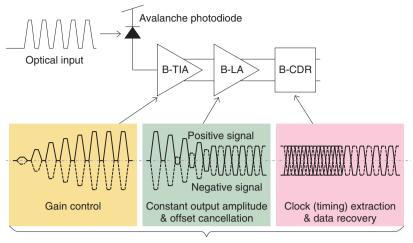

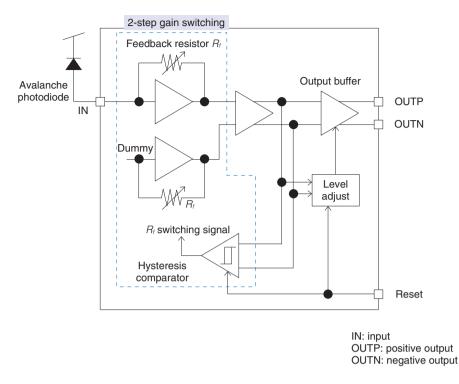

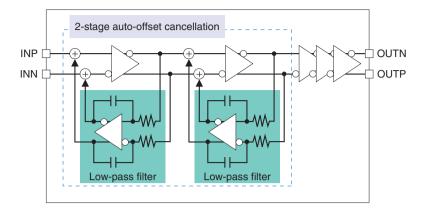

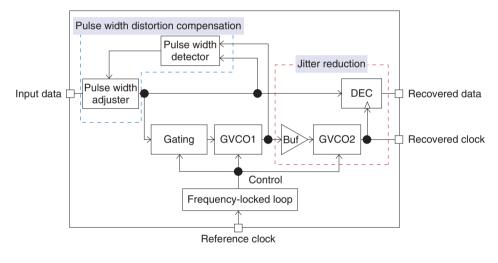

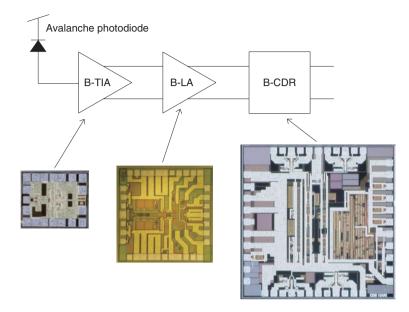

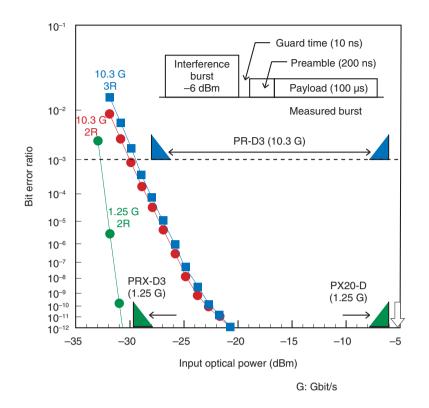

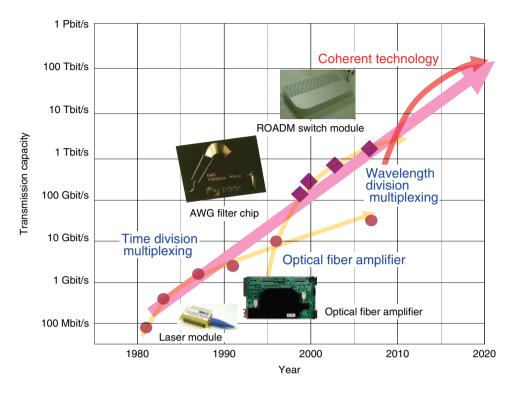

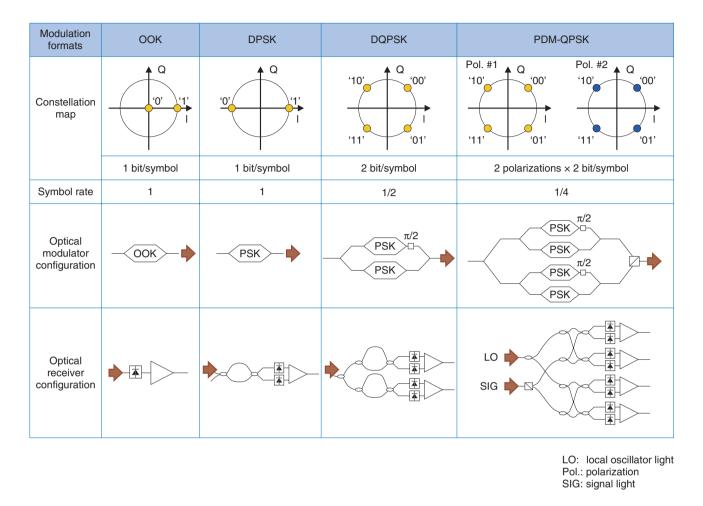

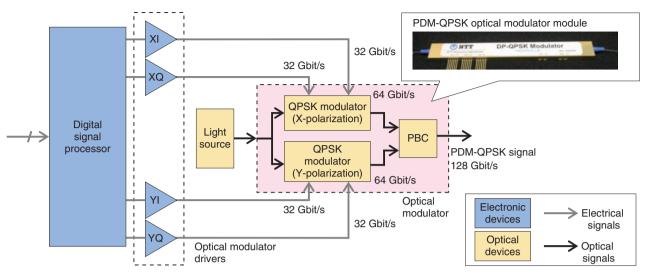

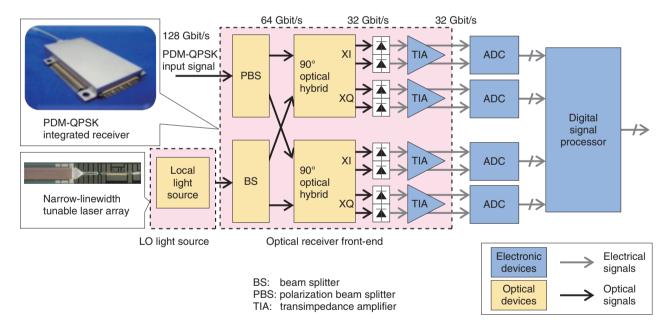

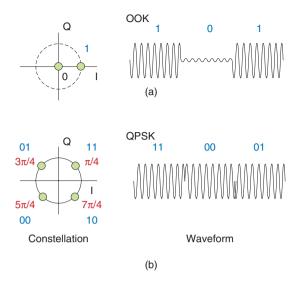

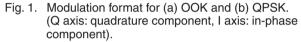

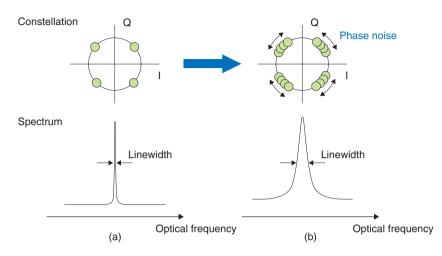

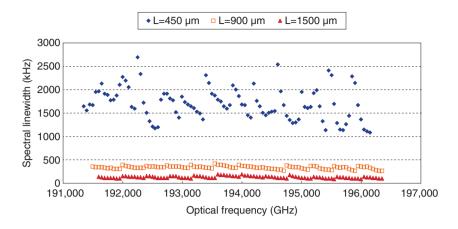

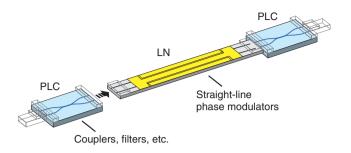

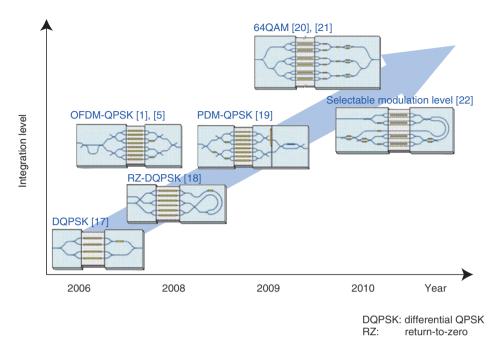

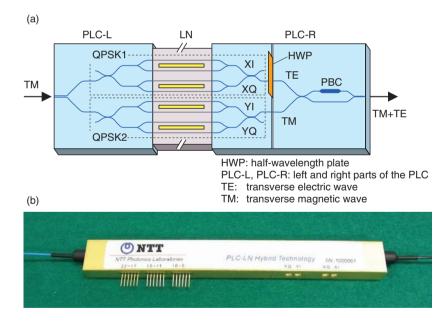

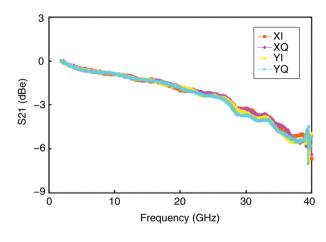

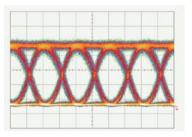

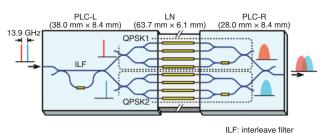

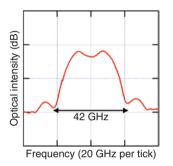

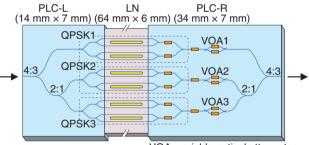

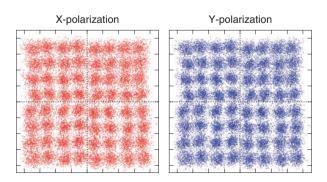

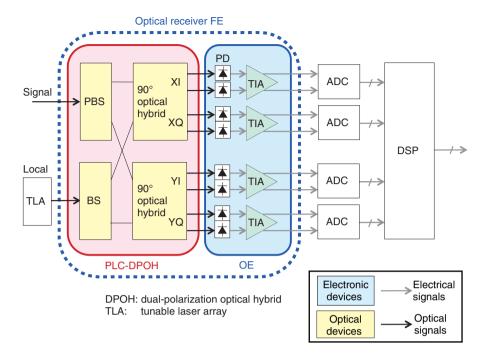

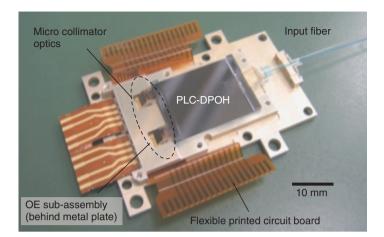

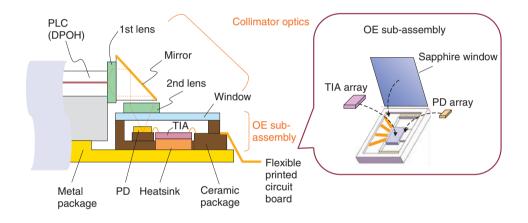

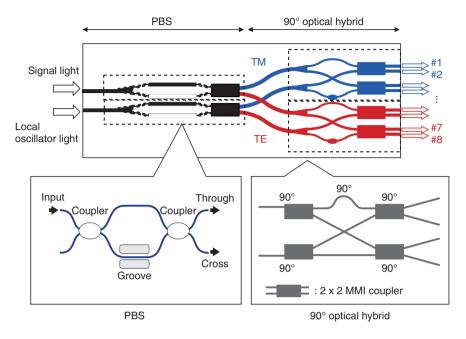

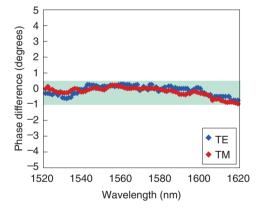

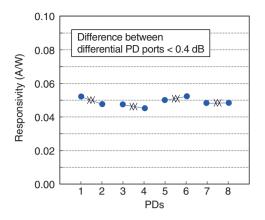

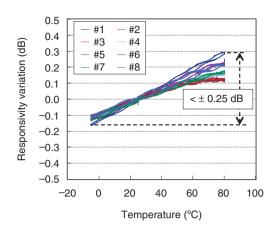

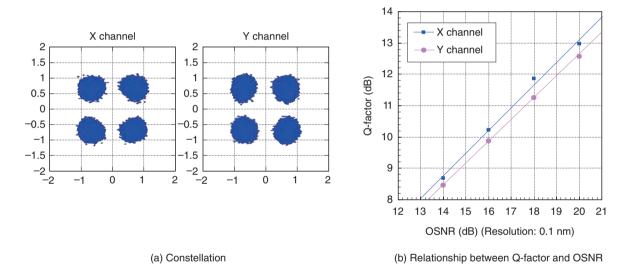

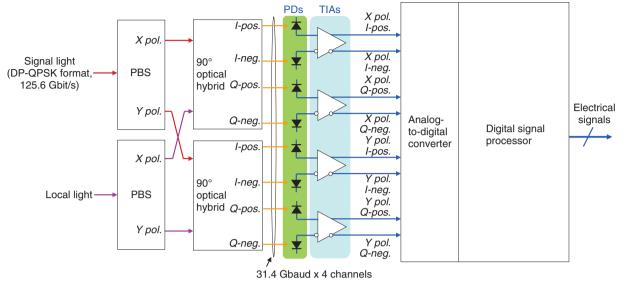

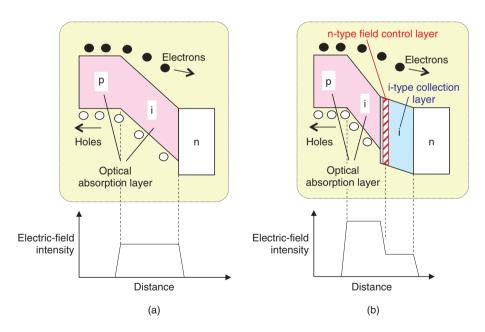

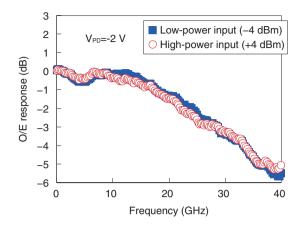

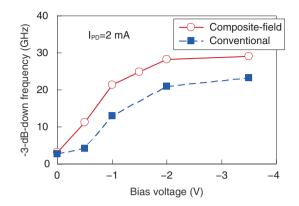

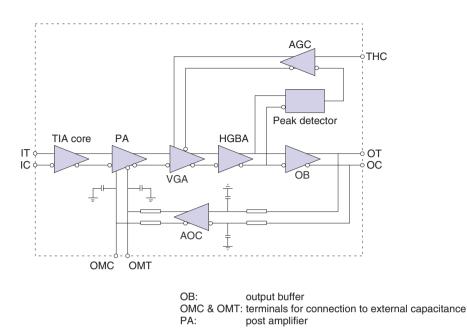

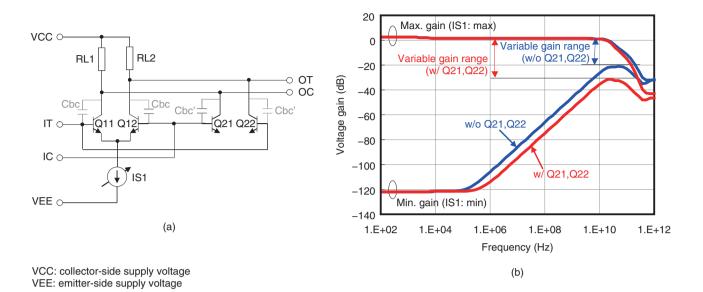

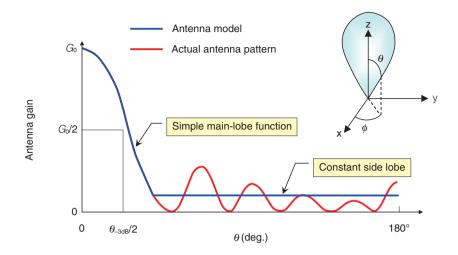

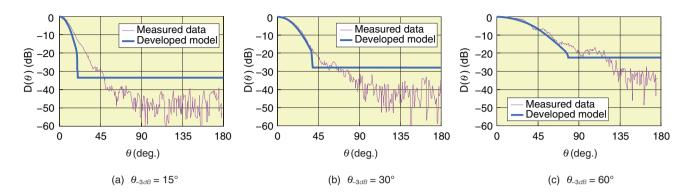

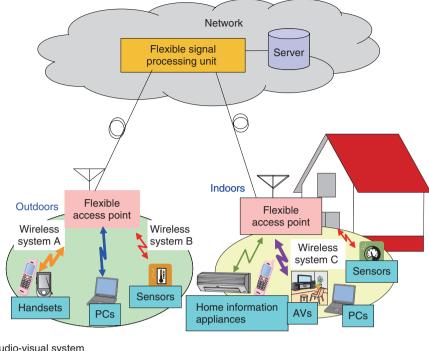

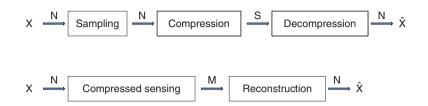

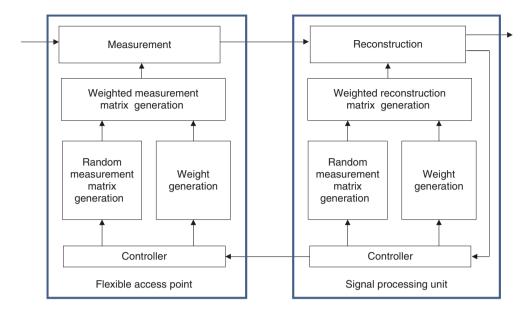

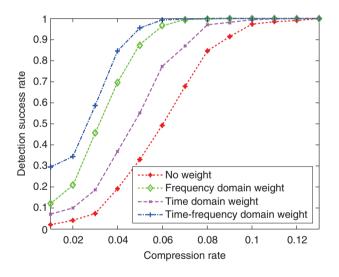

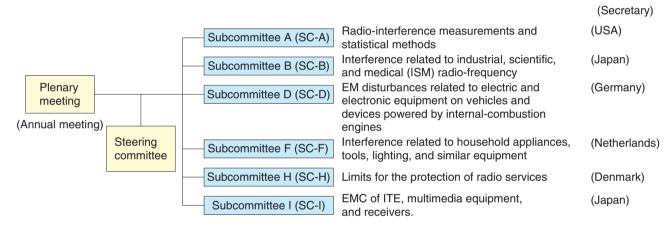

Fig. 1. SoC design flow.