|

|||||||||||||

|

|

|||||||||||||

|

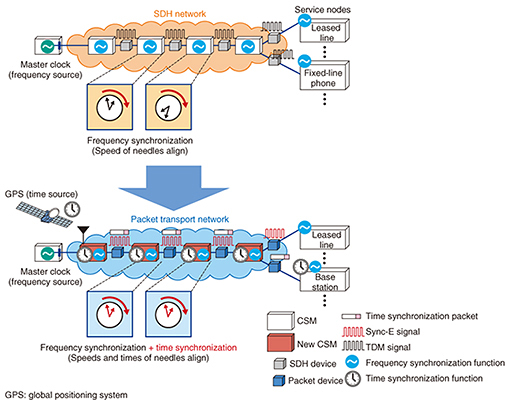

Regular Articles Vol. 15, No. 10, pp. 54–59, Oct. 2017. https://doi.org/10.53829/ntr201710ra3 Practical Implementation of a New Clock Supply Module Supporting Telephone System Communications and Leased Line Communications for Corporate CustomersAbstractNTT has achieved high-accuracy frequency synchronization for communications using time division multiplexing, which is applied to telephony, leased lines, and other applications. Recently, the demand for high-accuracy time synchronization as well as high-accuracy frequency synchronization has increased, particularly in mobile systems. We introduce here the New Clock Supply Module (New CSM) enabling high-accuracy frequency and time synchronization on packet transport networks. Keywords: clock supply module, time synchronization, phase information transmission 1. IntroductionServices such as fixed-line telephony and digital leased lines are currently provided on networks using time division multiplexing (TDM). TDM requires that the frequency of each system on the network be aligned with a high degree of accuracy for digital demultiplexing. At present, this is achieved by constructing a clock path network using a clock supply module (CSM), providing frequency synchronization over the entire network. This means that services requiring frequency synchronization must be continuously connected to a CSM and clock path network. In existing clock path networks, the frequency information is transmitted using a synchronous digital hierarchy (SDH) transmission system between the master clock, which is a high-accuracy frequency source for the highest-hierarchy building, and a CSM installed in each building (SDH network), as shown in Fig. 1. Additionally, a redundant configuration using N (normal) and E (emergency) paths is used in order to achieve high reliability. If frequency information on the N path is disrupted, it will automatically be switched to the E path, providing stable frequency synchronization. Consequently, support for various transmission systems is essential in order to efficiently construct a clock path network with route distribution. Additionally, a migration to packet transport technologies on the transmission system also requires support in clock path networks.

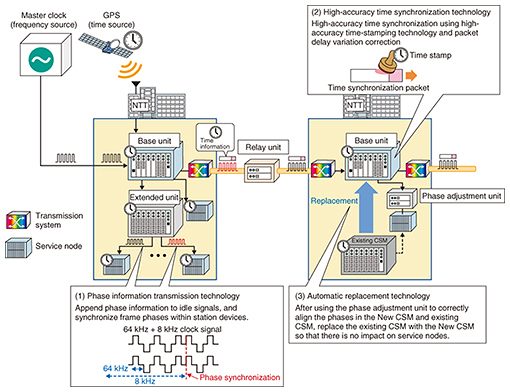

Furthermore, in recent years, we have seen an increase in the number of services that require time synchronization of systems within a network, meaning an expansion in the application of network synchronization technologies. For example, the field of mobile communications requires time synchronization with a margin of error within the double-digit nanoseconds in order to provide support for broadband services using 5G (fifth-generation mobile communications networks) [1]. Against this background, we have developed a New Clock Supply Module (New CSM) that can transmit frequency information and phase information on the packet transport network and provide high-accuracy time synchronization. The New CSM comprises four units—a base unit, an extended unit, a relay unit, and a phase adjustment unit—as shown in Fig. 2. The base unit is synchronized with the master clock (frequency source), GPS* (time source), and the upper CSM, transmitting frequency information and time information. The extended unit extends the capacity of service nodes such as switching equipment and leased line equipment. The relay unit extends the distance over which frequency information and time information can be transmitted. The phase adjustment unit makes it possible to efficiently replace an existing CSM with the New CSM. The distinctive technologies in these units provide phase information transmission, high-accuracy time synchronization, and automatic replacement functions. We explain these in more detail in the following sections.

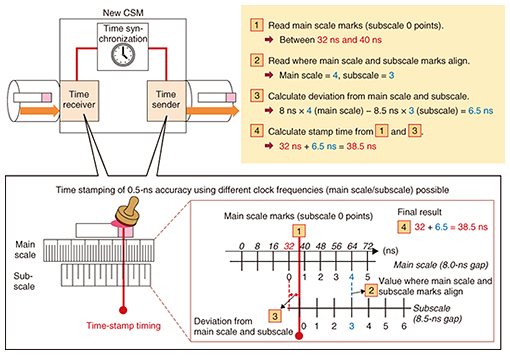

2. IssuesFirst, we describe some issues that need to be resolved regarding the technologies mentioned in the previous section. 2.1 Necessity of phase information transfer in addition to frequency informationMethods of transmitting frequency information on packet transport networks are standardized as Synchronous Ethernet (Sync-E) technology [2–4]. Sync-E technology enables transmission of frequency information without the effects of electrical noise. However, when some devices communicate with other devices in the same building, some service nodes that receive frequency information require that frame header timing be aligned. Therefore, it is necessary to synchronize phases as well as frequencies. In packet transport networks, when phase information is transmitted using packets, the effects of other packets will generate time fluctuations in transmission and reception cycles, preventing high-accuracy phase information transmission. 2.2 Support for high-accuracy time synchronizationTime synchronization methods are standardized as Precision Time Protocol (PTP), a time synchronization protocol that can be used on packet transport and other networks [5]. PTP provides bidirectional exchange of time synchronization messages in networks consisting of a master node and a slave node, and it corrects the time offset of a slave node to the master node. Time synchronization messages store time-stamp information detailing transmission/reception times, and PTP uses this time-stamp information to calculate the time offset. Time-stamp information is assigned using hardware processing within the devices. However, there may be an error between the original time-stamp information and the assigned time depending on the hardware processing performance. This error in the time-stamp information has a direct impact on the accuracy of time synchronization and therefore needs to be reduced. Additionally, as one of the synchronization conditions, PTP must presuppose an equivalent time delay in both directions. Accordingly, utilizing PTP in a configuration in which master and slave nodes are connected using transmission systems may adversely affect the accuracy of time synchronization. This is because random time delay variations may occur as a result of packet processing conflicts within transmission systems. Accordingly, high-accuracy time synchronization requires a reduction of the time error resulting from delay variations. 2.3 Rapid replacement of existing CSM with New CSMConstruction of a clock path network using the New CSM requires replacement of the existing CSM. If this process is supported only by changing the connection of the clock transmission cable, the frequency synchronization can be achieved between the existing CSM and the New CSM. However, since it is not possible to accurately match the phase information before and after the replacement, the phase jumps at the service node receiving the phase information, which may affect the quality of service. When replacing an existing clock system of the previous generation with a current CSM, operators carry out phase alignment manually by monitoring waveforms on an oscilloscope. However, a quicker, more accurate way to align phases is required when replacing several thousand existing CSMs with the New CSM. 3. Technical points in resolving issuesHere, we discuss the technical requirements to resolve the above issues. 3.1 Phase information transmission technologyIn packet networks, transmission of frame signals requires that noncontiguous idle signals be sent whenever frame signals are not sent. Idle signals can be transmitted without being dependent on the transmission/reception status of packets. Therefore, the New CSM focuses on these idle signals. Using a phase information transmission method that replaces some idle signals with other idle signals (phase idle signals) that do not violate rules enables the transmission of accurate phase information. 3.2 High-accuracy time synchronization technologyTo resolve the problematic time errors caused by the time-stamping error and the delay variation from linked system devices, the New CSM implements a time-stamping method using a Vernier scale and a packet delay variation correction method through the accumulation of statistical distribution data to achieve high-accuracy time synchronization. (1) Time-stamping method using Vernier scale The time-stamping error is affected by the internal clock frequency of the device. For example, if the internal clock frequency is 100 MHz, a time-stamping error of a maximum of 10 ns may be generated. Since there is a physical limit to increasing the internal clock frequency, it is inevitable that a certain amount of time-stamping error will occur. In response to this problem, the New CSM drastically reduces the time-stamping error by using two internal clock frequencies. This is a method called the Vernier scale, in which two internal clocks are used as a main scale and subscale. Altering the interval between these scales enables values to be read with high resolution (Fig. 3). With this method, time-stamping errors can be reduced to within 0.5 ns.

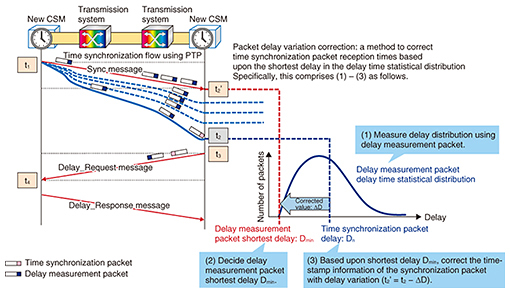

(2) Packet delay variation correction method through accumulation of statistical distribution data Reducing time synchronization errors resulting from delay variations generated in a transmission device requires correction of the reception time of time synchronization packets, so that delays in both directions are equivalent. Averaging the reception time of time synchronization packets has been the conventional way to correct the reception time. This method is effective if there is a constant average delay in both directions. However, because the traffic of user packets changes from moment to moment, the average value of the bidirectional delay time does not necessarily match. Accordingly, the New CSM measures the actual delays in multiple delay measurement packets. Then it statistically ascertains the delay variation characteristics, enabling correction of delay variations in time synchronization packets (Fig. 4).

3.3 Automatic replacement technology from existing CSM to New CSMTo achieve accurate phase matching between the existing CSM and New CSM in a short time period during the replacement process, the New CSM has an automatic phase adjustment function and performs appropriate phase difference correction by running algorithms using parameters such as the waveform characteristics of New CSM and the current CSM, the connection cable length, and the amount of internal delay. Additionally, the accuracy of the work is increased during the parameter input by simplifying the setting work, visualizing the setting procedures, and installing control applications that enable warning notifications in the event of problems. With this function, it is possible for the operator to achieve phase alignment on the order of nanoseconds simply by inputting the necessary parameters. 4. Future prospectsWe introduced the New CSM developed by NTT Network Service Systems Laboratories that includes technologies for phase information transmission, high-accuracy time synchronization, and automatic replacement of CSM. Going forward, we plan to offer trouble-free, ongoing assistance targeting the introduction and operation of the New CSM, and we will carry out research and development to meet higher accuracy requirements. References

|

|||||||||||||